Durante años, la evolución de la electrónica ha seguido un principio sencillo: mientras más pequeño, mejor. Desde los años 60, cada nueva generación de chips ha logrado empaquetar más transistores en menos espacio, alineándose con la famosa ley de Moore. Formulada por Gordon Moore, cofundador de Intel, esta ley predecía que la cantidad de componentes en un microchip se duplicaría anualmente. Sin embargo, esa búsqueda de lo diminuto ha encontrado sus límites físicos. Un equipo internacional de científicos ha propuesto una solución sorprendente: en lugar de seguir reduciendo el tamaño de los chips, ¡construyamos hacia arriba!

Un Chip de 41 Capas

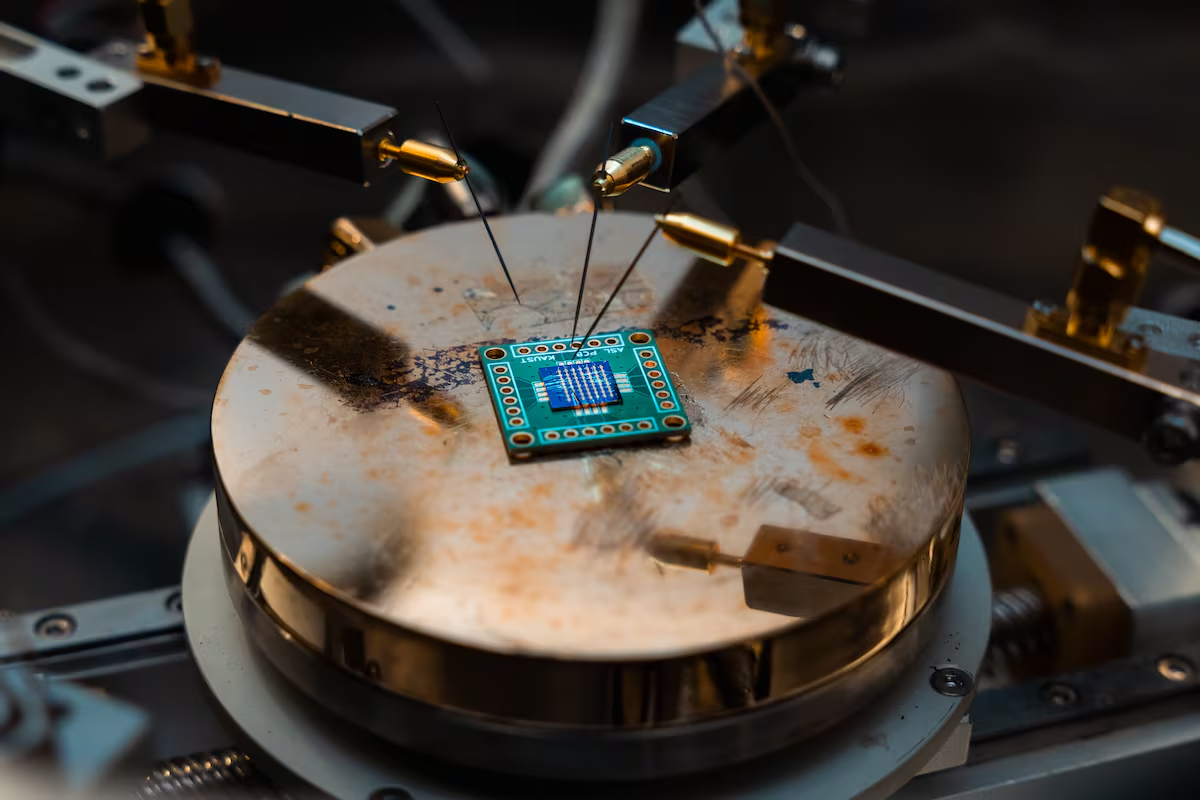

Xiaohang Li, investigador de la Universidad de Ciencia y Tecnología Rey Abdullah (KAUST) en Arabia Saudí, lidera un equipo que ha diseñado un chip con impresionantes 41 capas verticales de semiconductores y materiales aislantes, ¡diez veces más alto que cualquier chip fabricado hasta ahora! Este innovador trabajo, publicado recientemente en la revista Nature Electronics, no solo representa un hito técnico, sino que también abre las puertas a una nueva generación de dispositivos electrónicos flexibles y sostenibles.

“Apilar seis o más capas de transistores verticalmente nos permite incrementar la densidad de circuitos sin necesidad de hacer los dispositivos más pequeños”, afirma Li. “Con solo seis capas, podemos integrar un 600% más de funciones en el mismo espacio que con una sola capa, mejorando el rendimiento y reduciendo el consumo energético”.

La Evolución de la Ley de Moore

Desde alrededor de 2010, la ley de Moore empezó a perder fuerza a medida que los fabricantes de chips se hallaron ante los límites impuestos por la física. Actualmente, los transistores son tan pequeños que los efectos cuánticos comienzan a afectar su funcionamiento. “La ley de Moore está alcanzando sus límites en la microelectrónica convencional de silicio, pero seguimos innovando. En lugar de reducir los transistores, estamos explorando nuevos materiales y arquitecturas, así como el concepto de apilamiento”, explica Li.

Rascacielos de Transistores

Li usa una metáfora arquitectónica para ilustrar el desafío al que se enfrentó su equipo: “Imagina que cada capa de transistores es como un piso de un rascacielos. Si un piso es irregular, toda la estructura se vuelve inestable”. El éxito de este experimento dependería de controlar la “rugosidad de la interfaz”; cualquier mínima imperfección entre las capas podría interrumpir el flujo de electrones y disminuir considerablemente el rendimiento del chip.

Un avance clave fue conseguir que todas las capas se depositaran a temperaturas cercanas a la ambiente. “Muchos materiales flexibles no pueden soportar altas temperaturas, y los procesos de semiconductores tradicionales superan los 400 °C, lo que dañaría estos materiales. Mantener la temperatura cerca de la ambiente permite usar sustratos de plástico o polímeros, lo que abre la puerta a la electrónica flexible del futuro”, detalla Li.

Impresionantes Resultados y Futuras Aplicaciones

El equipo fabricó 600 copias del chip, todas con un rendimiento consistente. Al utilizar estos chips apilados para realizar operaciones básicas, lograron un rendimiento similar al de los chips convencionales pero con un consumo notablemente inferior: solo 0.47 microvatios, en comparación con los típicos 210 de los dispositivos de última generación.

¿Dónde podríamos ver esta revolucionaria tecnología aplicada por primera vez? Li se muestra optimista pero realista: “Los sensores de salud portátiles, las etiquetas inteligentes y las pantallas flexibles serán las primeras aplicaciones. En el futuro, imaginamos superficies informáticas extensas, o «pieles electrónicas», que podrían sentir y comunicarse a través de objetos enteros”. Aunque estos nuevos chips quizás no alimenten supercomputadoras, su implementación en electrodomésticos podría reducir significativamente la huella de carbono de la industria electrónica.

Los circuitos desarrollados están diseñados para sistemas donde la flexibilidad, el bajo coste y la escalabilidad son más relevantes que una velocidad extrema. “Esta investigación abre una nueva puerta en informática”, concluye Li: “Demuestra que el rendimiento puede seguir escalando no solo haciendo los dispositivos más pequeños, sino integrándolos de una manera más inteligente y eficiente en tres dimensiones”.